# The CAD Library

by Tom Hausherr

Tom Hausherr, CID+, has been involved in the design and development of PCB electronics since 1974. He is currently the EDA Library Product Manager for Mentor Graphics Corporation. He has received a number of awards for his work in PCB Standards Development including three IPB "Awards of Excellence" and a DesignVision award in 2007 for Best New CAD Software Tool. Before joining Mentor Graphics, Tom owned a PCB layout service bureau and was CEO, Director of Technology for PCB Matrix Corp. To date, Tom has developed more than 2000 PCB products.

http://www.pcbdesign007.com/pages/columns.cgi?clmcatid=&clmid=58

# Introduction

This is a series intended to help the reader create a high-quality CAD library. The CAD library is the starting point that affects every process from engineering and PCB layout through PCB manufacturing and assembly.

#### **Guidelines and Recommendations**

When creating a CAD library, there are dozens of things to consider that are often overlooked or not even considered that will directly affect the quality of part placement, via fanout, trace routing, post processing, fabrication, and assembly processes. This article, Part 1 of a series, introduces aspects that should be considered when creating CAD library parts and the impact that each feature of the CAD library has on the PCB process. Subsequent articles will delve more deeply into these concepts.

A high-quality CAD library can make a huge difference in the quality of your PCB design layout and your overall productivity levels throughout the PCB design process. Also, you must have the necessary tools that can quickly build new CAD library parts – parts that are consistent in quality, with identical features in every library part. You also need an organized CAD library management system that allows you to quickly locate the correct land pattern for each component in your PCB layout.

To begin, all of the components and their related land patterns can be found in the free LP Viewer that you can download by clicking <u>here</u>.

#### **Creating a CAD Library**

Creating a CAD library requires answers to these questions:

Why do we snap the lands (pads) to a 0.1 mm grid?

Why is the assembly outline different than the silkscreen outline?

Why do we snap the via fanout to a 1 mm grid?

Why is it important to use metric units when creating your CAD library?

What is the IPC-7351B standard and why is it important?

Every good PCB designer has the heart of an artist and the mind of a mathematician, and each PCB design is a different piece of art with mechanical precision. Good PCB designers take pride in their workmanship as they strive to make each new PCB layout more perfect than the last. After 35 years of laying out over 2,000 PCB designs, I can say without any reservation that PCB design perfection starts in the CAD library.

#### **Measurement Units**

One of the secrets of today is that 90% of all component manufacturers are providing their component package dimensions and pin pitches in metric units. Texas Instruments only provides metric units for all 982 of their component packages. TI is following the metric mandate set by all world standards organizations and 99% of all world governments. So your CAD library should also be built using metric

units.

Using metric units for PCB design layout is the future, so you should transition to metric as soon as possible and quit wasting your time building an Imperial unit working environment. The longer you wait to transition, the harder it becomes. If you're a PCB design artist in search of perfection, this series of columns will clearly illustrate why metric units for PCB layout is vastly superior.

# The IPC-7351B Standard

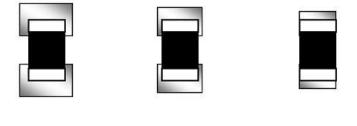

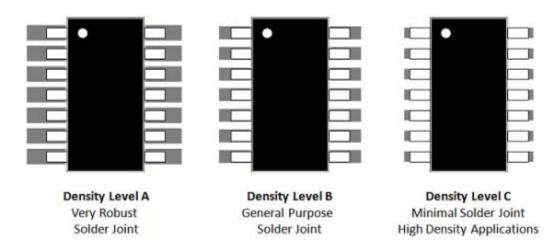

Let's briefly look at the IPC-7351B Standard. We will reference this standard throughout the series. IPC-7351B standard uses a 3-Tier CAD library system:

Most land protrusion (Density Level A) – for military and medical applications

Nominal land protrusion (Density Level B) - for controlled environment desktop

Least land protrusion (Density Level C) - for cell phones and hand held devices

The IPC-7351B standard focuses on these key items:

Land size and spacing calculations

Placement courtyard boundary

Land pattern name

Zero component orientation

Padstack name

Three types of CAD library parts are defined: Plated through-hole (PTH), surface mount devices (SMD), and a combination of the two technologies. SMD and PTH CAD libraries are distinctively different but the same basic rules apply to both technologies – "snap" and "round-off" CAD library land (pad) shapes are defined in 0.05 mm increments.

We will look at why this standard is so important and how it relates to our CAD library shortly in the series.

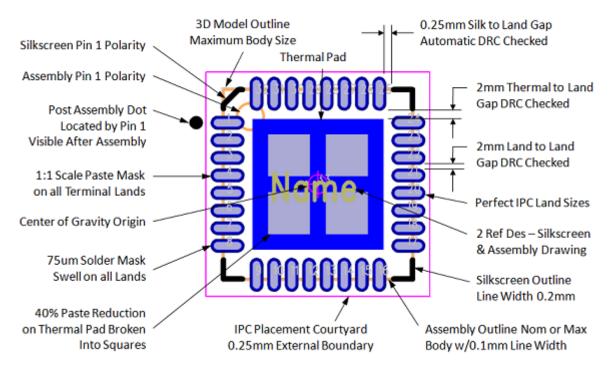

In addition to the items in the IPC-7351B standard, other important considerations are basic guidelines and drafting recommendations for your CAD library. These are summarized here and will be fully explored as we continue.

Pad spacing with DRC checking and pad trimming when necessary

Pad size and space round-off

Four outlines

Silkscreen

Assembly

Placement courtyard – adjustable sizing for IPC 3-Tier environment levels

# 3D model

Polarity Markings for both silkscreen and assembly

Two reference designators with center/center justification (Ref Des Origin), right reading orthogonal, located at the land pattern origin with height 1.5 mm and line width 10% of Height

# The 1608 (EIA 0603) Chip Component

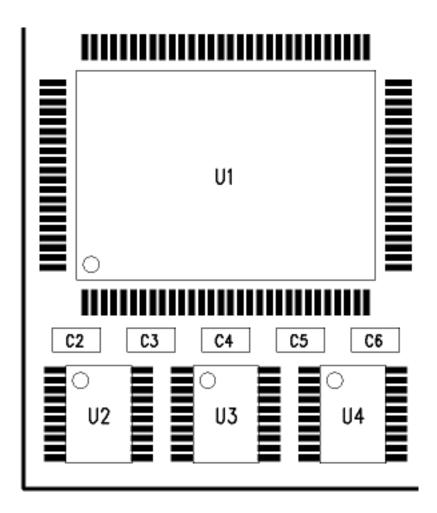

Chip components make up the majority of the parts on a normal PCB layout. These chip components have a "wraparound" lead form. My last PCB layout had 698 capacitors, 386 chip resistors, and 81 chip inductors. The entire design had 1,250 parts and 1,165, or 93%, were chip components. So, it is very important that we address chip components first in this series.

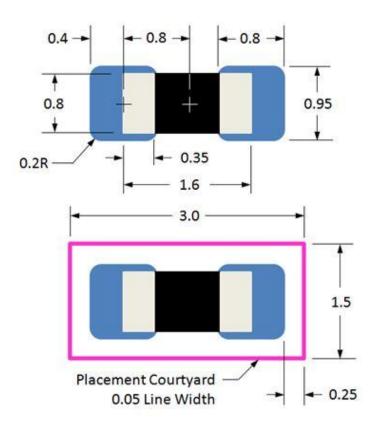

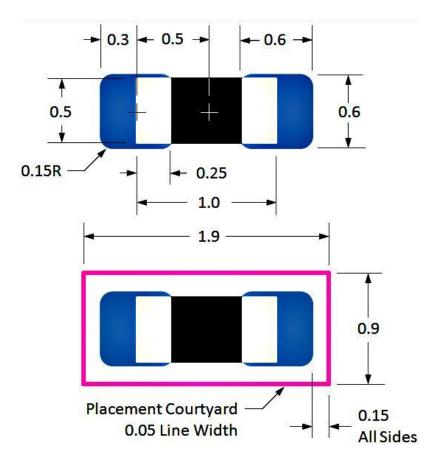

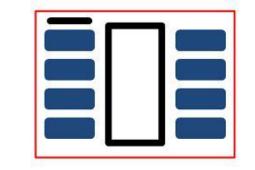

The majority of chip components are metric by design, i.e., 90% of all chip component dimensions are whole metric values. See Figure 1 for the dimensions of a standard 1608 (EIA 0603) component superimposed with its related land pattern (in blue) and placement courtyard excess of 0.25 mm. Notice that the placement courtyard is 3.0 mm X 1.5 mm. That dimension is perfect for placing this land pattern using a 0.5 mm grid system — they all line up perfectly.

The land size and centric placement are rounded in 0.05 mm increments to enhance trace routing using a 0.05 mm routing snap grid and trace widths in 0.25 mm increments.

# Figure 1. Standard 1608 (EIA 0603) component superimposed with its related land pattern (in blue) and placement courtyard excess of 0.25 mm.

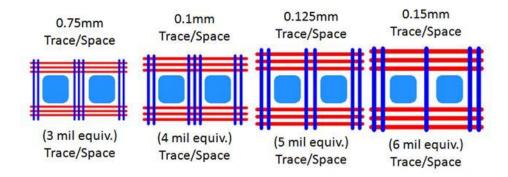

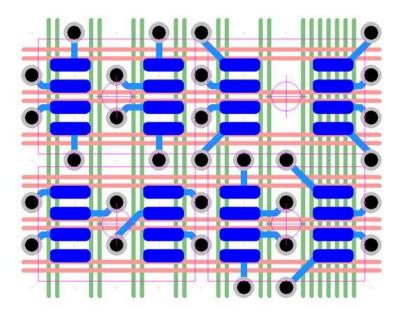

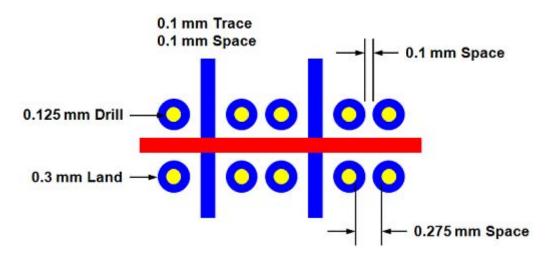

Figure 2 illustrates four of the most popular trace/space routing technologies that use a 0.05 mm routing grid. The six most popular metric trace widths rounded in 0.25 mm increments are:

- 1. 0.075 mm (3 mils)

- 2. 0.1 mm (4 mils)

- 3. 0.125 mm (5 mils)

- 4. 0.15 mm (6 mils)

- 5. 0.2 mm (8 mils)

- 6. 0.25 mm (10 mils)

The main point that I am trying to make here is that with most CAD tools, using a PCB design grid system is best. One exception to this is the Mentor Graphics Expedition Enterprise, which handles gridless solutions. But for users of other industry tools, building CAD libraries, part placement, via fanout and trace routing using specific snap grids greatly enhances the speed and quality of the PCB layout.

The standard universal grid system today is 0.05 mm, but at times 0.025 mm increments need to be used specifically for trace/space rules.

The next generation of grid systems in the near future will be 0.01 mm, which I refer to as "high resolution." There will likely never be a need to go more than 2 places to the right of the decimal point for any PCB design feature values.

Figure 2. Comparison of four popular trace/space routing technologies that use a 0.05 mm routing grid.

The same chip component technology can be applied to every chip resistor and capacitor used in the industry today. The most relevant aspect of this technology is that a 0.1 mm placement grid and a 0.05 mm routing grid system produce optimized results regardless of the trace/space technology, because the land (pad) center snap grid is 0.05 mm from the origin and the land (pad) size round-off values are in 0.05mm increments.

# Fanout

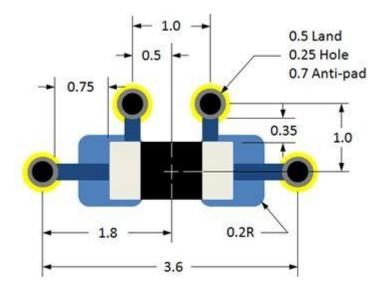

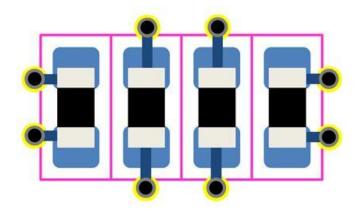

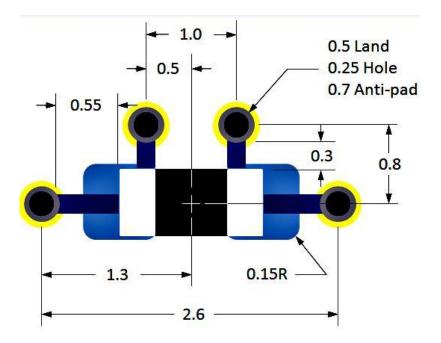

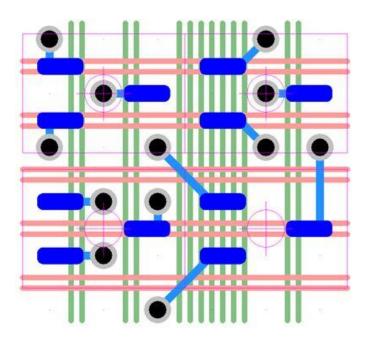

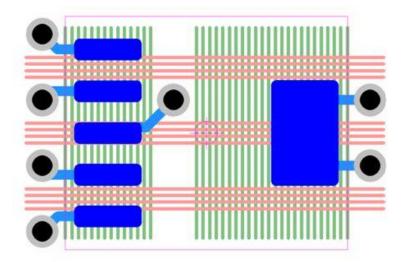

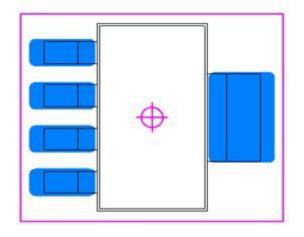

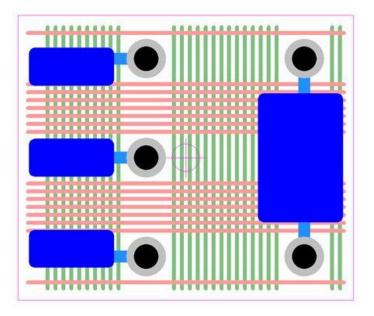

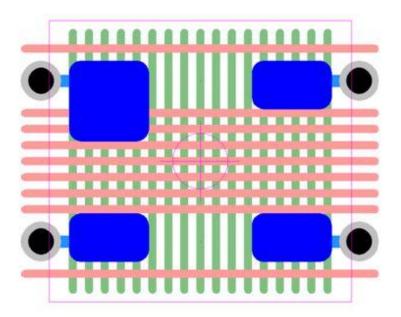

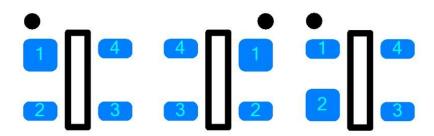

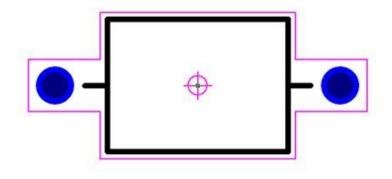

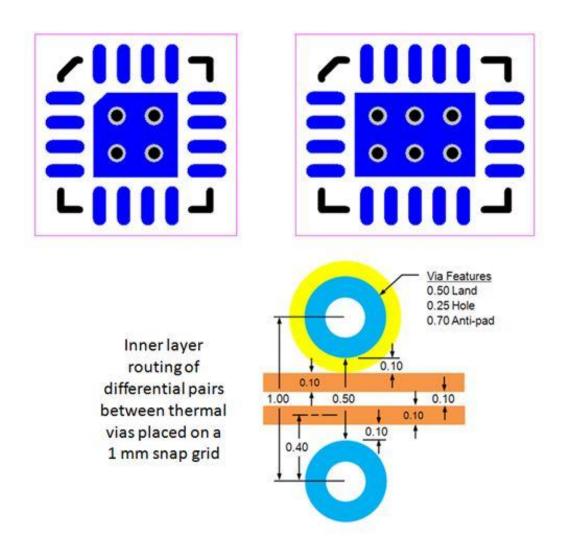

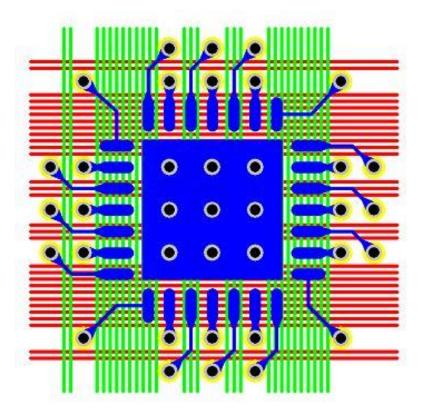

Let's talk about via fanout solutions for the same 1608 (EIA 0603) chip capacitor. In Figure 3 you can see two different fanout options, and one is superior to the other. The fanout coming out the top has all the key features. The vias are 0.4 mm closer to the capacitor component terminals than the typical right/left fanout, which decreases impedance and increases capacitance.

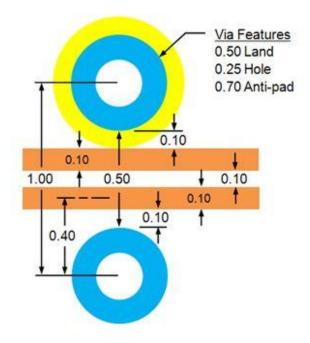

Also, the top fanout vias snap to a 1 mm grid because the 1608 land pattern was snapped to a 0.5 mm grid system. The 0.5 mm via land (pad) diameter with 0.25 mm hole size and 0.7 mm plane anti-pad is perfect for 0.1mm trace/space technology. See Figure 4 for the routing solutions. The trace width for the power fanout is 0.3 mm.

Figure 3. Two different fanout options.

Figure 3 clearly illustrates the superior routing channels between two vias placed on a 1 mm snap grid. This same example can be used for all chip and molded body resistors and capacitors. It is important to note that the plane anti-pad clearance does not infringe on the trace. The trace requires a clean uninterrupted return path on the adjacent reference plane. This via land, hole size, and trace/space technology is very easy to manufacturer and does not require additional fabrication cost.

# Figure 4. Graphic depicting routing solutions.

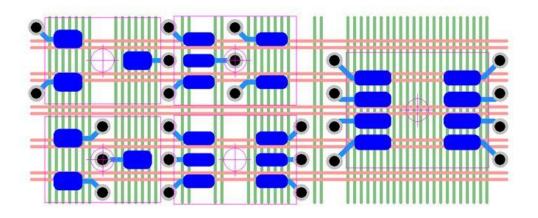

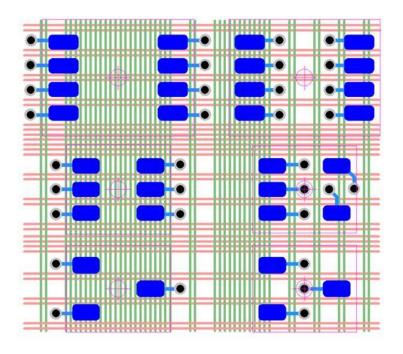

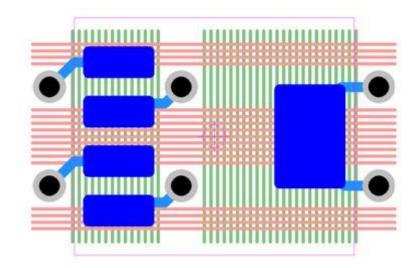

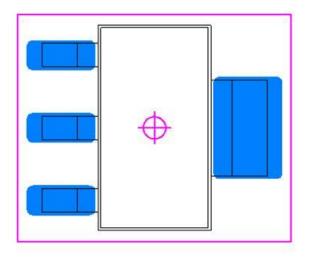

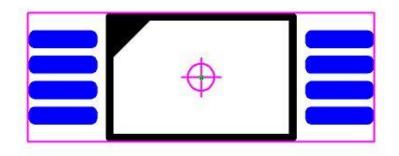

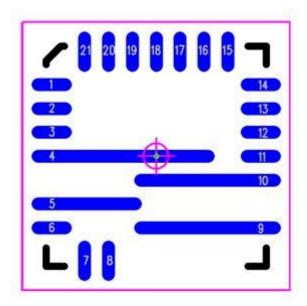

The part placement of the 1608 (EIA 0603) can use a 0.5 mm snap grid and the placement courtyards can be placed side by side. The via fanout can be a 1 mm snap grid when exiting the side of the land pattern; otherwise, when exiting the top and bottom, a 0.1 mm snap grid can be used. See Figure 5 for

the placement and fanout example for the 1608 (EIA 0603) chip components. Side via fanout is superior for bypass capacitors connecting to the planes and best for 1 mm via snap grid. The top and bottom fanout is OK for signal resistors.

Figure 5. Placement and fanout example for the 1608 (EIA 0603) chip components.

# **Components Smaller Than 1608 (EIA 0603)**

When chip component sizes are smaller than 1.6 mm X 0.8 mm, the IPC-7351B standard defines seven rule changes that every PCB designer and CAD librarian must be aware of:

The land (pad) snap grid changes from 0.1 mm to 0.02 mm

The land size round-off changes from 0.05 mm to 0.01 mm

The toe goal changes from 0.35 mm to 0.2 mm

The corner radius changes from 0.2 mm to 0.15 mm

The courtyard excess changes from 0.25 mm to 0.15 mm.

When entering the component min/max dimensions the "nominal" terminal dimensions are used for both the min & max fields

The part placement grid changes from 0.5 mm to 0.1 mm

#### 1005 (EIA 0402) Design

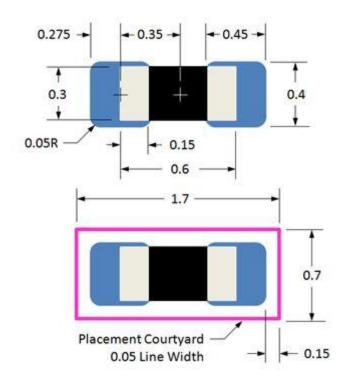

See Figure 1 for the dimensions of a standard 1005 (EIA 0402) component superimposed with its related land pattern. In this case, I decided to break the rules:

Land size round-off 0.05 mm

Land snap grid round-off 1.0 mm

Tighten the tolerance on the component width (W = 0.5 mm) to +/-0.05

The land-center to land-center spacing is 1.0 mm, which is perfect for 1.0 mm space via fanout. And the placement courtyard width is 1.0 mm, which is perfect for placing parts 1.0 mm from center to center. When placing the 1005 (EIA 0402) in the PCB layout, use a 0.1 mm grid to optimize the part placement and via fanout.

Figure 1. A standard 1005 (EIA 0402) component superimposed with its related land pattern.

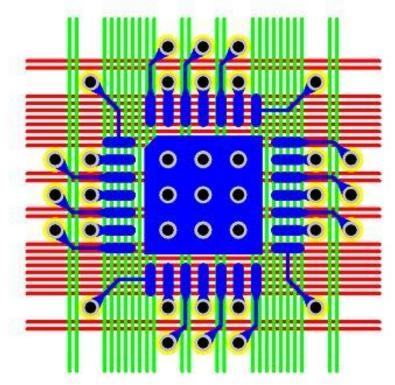

The 1005 (EIA 0402) was made for 1 mm pitch BGA fanout. In Figure 2 you can see two different fanout options; one is superior to the other. The fanout coming out the top has all the key features. The vias are 0.25 mm closer to the capacitor component terminals than the typical right/left fanout, which decreases impedance and increases capacitance. Also, the top fanout vias snap to a 1 mm grid because the 1005 land pattern was snapped to a 0.1 mm grid system. The 0.5 mm via land (pad) diameter with 0.25 mm hole size and 0.7 mm plane anti-pad is perfect for 0.1mm trace/space technology. The trace width for the power fanout is 0.3 mm.

# 0603 (EIA 0201)

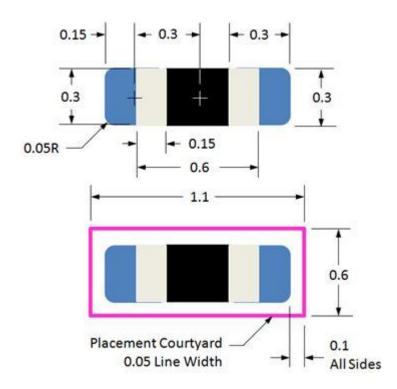

Figure 3 shows the dimensions of a standard 0603 (EIA 0201) component superimposed with its related land pattern. In this case, I decided to break the rules:

Land size round-off 0.05 mm

Land snap grid round-off 1.0 mm

Use the "Least" environment due to component miniaturization

For chip components smaller than 1.0 mm X 0.5 mm, I use the IPC-7351B "Least Environment" to prevent tombstoning. When two-pin micro-miniature parts have too much solder volume, tombstoning can occur in the reflow oven. The land size for the 0603 (EIA 0201) should be a minimum of two times the terminal lead size. The land maximum value is still being tested by assembly shops, as tombstoning is the Number 1 problem with the 0603 (EIA 0201) chip component.

Note: The placement courtyard width is 0.6 mm to compensate for the component width tolerance of +/-.03 mm.

Figure 3. A standard 0603 (EIA 0201) component superimposed with its related land pattern.

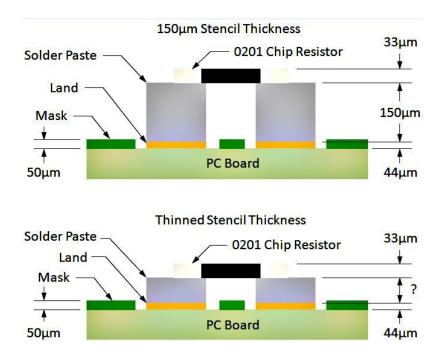

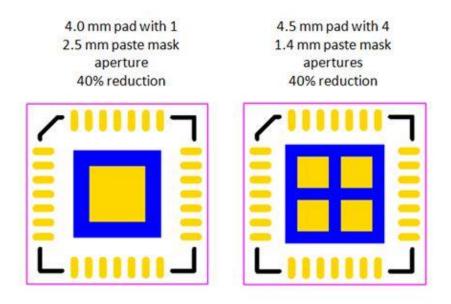

One of the techniques used to prevent tombstoning for the 0603 (EIA 0201) is to thin the paste stencil from 0.15 mm to a smaller value for every occurrence of this component in the paste mask stencil, as illustrated in Figure 4. The responsibility of the stencil thickness thinning process is placed on the assembly shop and the stencil manufacturer (not the PCB designer). Assembly shops use various solder alloys that require unique stencil creation.

# Figure 4. Thinning the paste stencil from 0.15 mm to a smaller value can prevent tombstoning for the 0603 (EIA 0201).

In Figure 5, the dimensions of a standard 0603 (EIA 0201) component are superimposed with its related land pattern. If you normally use the "Most" environment, my recommendation for the 0603 (EIA 0201) land pattern is to use the "Nominal" environment. The IPC nominal land size for the 0603 is about three times the size of the terminal lead. For this 0603 micro-miniature component, stay away from the "Most" environment as the solder volume is more than four times greater than the terminal lead footprint.

# Figure 5. A standard 0603 (EIA 0201) component superimposed with its related land pattern.

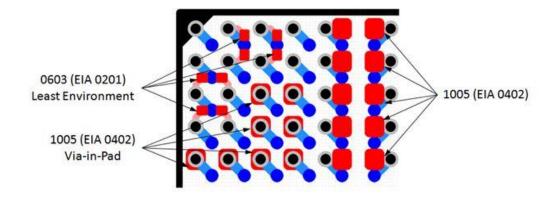

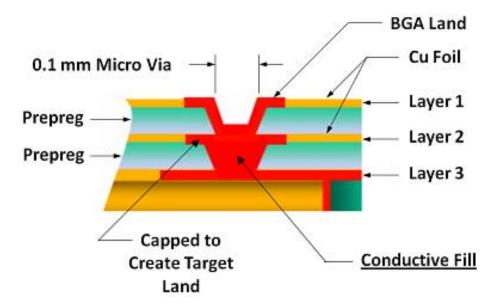

The 1005 (EIA 0402) & 0603 (EIA 0201) chip components are very compatible with 1.0 mm pitch BGA. In Figure 6 there are two different uses for the 1005 and one in between the vias and one via-in-pad method. Because the 1005 land centers are on 1.0 mm pitch, the capacitor land (pad) falls directly centered on the via. Via-in-pad technology will increase PCB cost because these vias need to be plated, filled and surface finish on the capacitor pad. The 0603 fall between the vias for the 0.1 mm trace/space technology DRC. This solution will not increase PCB fabrication cost. The dot grid display is 0.05 mm.

# Figure 6. Graphic detailing 1005 (EIA 0402) & 0603 (EIA 0201) chip components.

IPC does not have a "standard" on drafting items such as silkscreen and assembly outlines and polarity markings yet. There are several types of silkscreen outlines and polarity markings that are used for non-polarized chip parts, polarized capacitors, diodes and LED's.

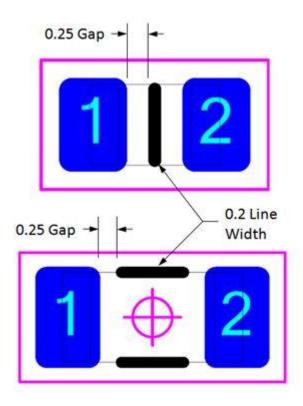

For a standard non-polarized chip, there are two options. See Figure 7 for both options. One is a line that separates the two lands. The default size is 0.2 mm and the default silkscreen land gap is 0.25 mm. The CAD librarian can change both the line width and the gap to achieve placing a line between two lands that only have a 0.3 mm gap by simply changing the line width and gap rules to 0.1 mm.

Figure 7. Two options available for standard non-polarized chips.

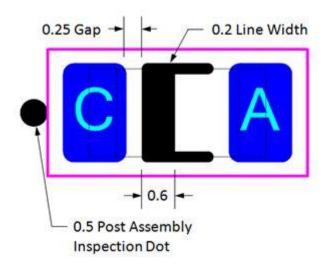

Figure 8 shows the silkscreen outline for the chip diode. The chip diode also features a post-assembly inspection dot so you can visually verify if the assembly inserted the diode or LED in the correct rotation. The polarized chip capacitor would have the same exact silkscreen outline but without the 0.6 mm bar.

# Figure 8. Silkscreen outline for the chip diode, showing the post-assembly inspection dot.

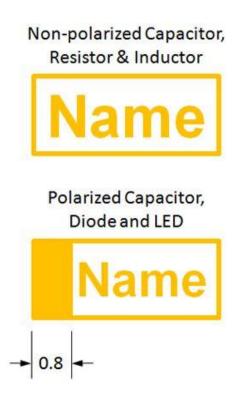

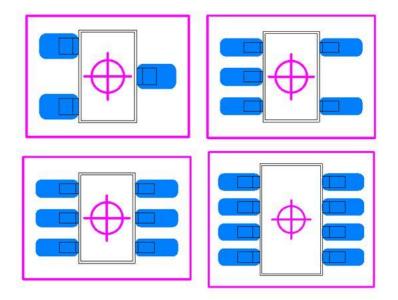

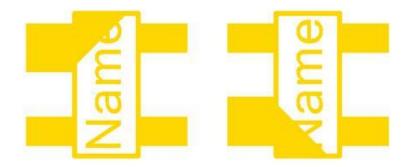

The assembly drawing outlines and polarity markings are totally different than the silkscreen outlines and polarity markings. The first most obvious difference is that the outline shape is 1:1 scale of the component body. This outline can be either the "Nominal" or "Maximum" component body size. Another difference is the reference designator is centered inside the component outline and is never moved or relocated. The reference designator default size is 1.5 mm height with a 10% line width.

The reference designator and assembly outline only change rules for micro-miniature parts. The assembly outline will grow as large as the placement courtyard in order to fit the reference designator inside the assembly outline. When the component gets smaller, the reference designator will decrease from the default 1.5 mm height to a sliding scale of values until it fits inside the assembly outline. The reference designator scaling width is always 10% of the height. The various reference designator heights for micro-miniature components are:

1.5 mm

1.25 mm

1.0 mm

0.75 mm

0.5 mm (this is the smallest human readable text height)

In Figure 9, the non-polarized and polarized capacitor, diode and resistor assembly outlines and reference designators are illustrated. Notice the absence of land pads. From all chip and molded body components, the land is removed from the SMT padstack to insure that the reference designators are unobstructed. Also, for CAD tools that have this feature, right reading orthogonal is always recommended so when the component is rotated, the reference designator is always flipped to right reading orientation.

Figure 9. Graphic depicting non-polarized and polarized capacitor, diode and resistor assembly outlines and reference designators.

# **Molded Body Components**

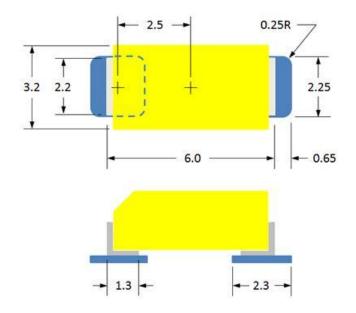

The next-most popular component family on a PCB design layout is the molded body tantalum capacitor (CAPM). The CAPM components have an "L-bend" component lead form. Most molded body tantalum capacitors are metric by default, including their standard EIA names:

3216 – 3.2 mm x 1.6 mm

6032 – 6.0 mm x 3.2 mm

7343 – 7.3 mm x 4.3 mm

Figure 1 illustrates the 6032 component and land pattern dimensions. I broke one rule to create this land pattern. Instead of a 1.0 mm land placement round-off I used a 2.0 mm land placement round-off to snap the land centers on a 0.5 mm grid from the center of the land pattern. When the land pattern is placed on a 0.5 mm grid, the land centers fall on a 0.5 mm grid. This improves the via fanout seen in Figure 3.

#### Figure 1. The 6032 component and land pattern dimensions.

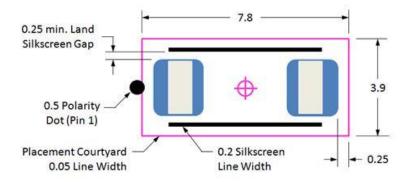

Figure 2 shows the silkscreen and placement courtyard rules and sizes. The illustration shows the component leads on top of the land for graphic representation.

Figure 2. The silkscreen and placement courtyard rules and size.

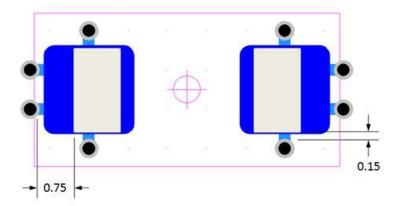

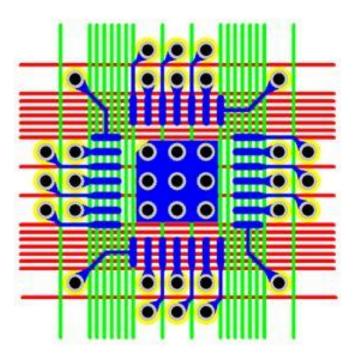

The via fanout for a 6032 tantalum capacitor is shown in Figure 3. If you are going to use the same size via to maintain trace/space compatibility with the rest of the PCB layout I recommend at least two vias. The placement of these vias is critical in accomplish reduced impedance and increased capacitance. It's important that the vias be placed as close as possible to the capacitor terminal leads.

In Figure 3, the two vias exiting the side are 0.15 mm away from the terminal lead. The vias coming out the ends on the land pattern are 0.75 mm away from the terminal leads. That's five times further away than the vias coming out the sides; however, some engineers will request all four vias. Since all the traces and vias are snapped to a 0.5 mm grid, this makes copy/paste much easier when manually designing fanout of the 6032 molded body capacitors. The dot grid display is 1.0 mm and the land pattern is placed on a 0.5 mm grid. All the vias in this illustration fall on a 1.0 mm snap grid.

Figure 3. The via fanout for a 6032 tantalum capacitor.

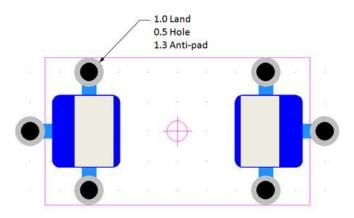

See Figure 4 for the 7343 molded body tantalum capacitor. I recommend a larger via size with a 1.0 mm land size, 0.55 mm hole size, and 1.3 mm plane anti-pad. This via can carry more current and you only need two (but the EE will ask for a third one). The illustration in Figure 4 snaps all the vias to a 1.0 mm grid system. These vias are twice the size of the previous vias but all the same trace/space rules apply. The display grid is 1.0 mm.

Because the land pattern, traces and the vias are on a 1.0 mm snap grid, this improves the copy/paste feature for manual fanout of all of the 7343 molded body components in your PCB layout.

Figure 4. Graphic depicting the 7343 molded body tantalum capacitor.

# **SOT23 Components**

The SOT23 is the most popular of the SOT component families. It features 3-, 5-, 6- and 8-pin variations and three popular pin pitches. Note: All pictures are shown in the "Nominal Environment" land pattern.

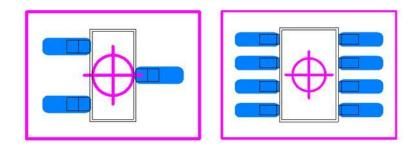

Figure 1 illustrates 0.5 mm pitch SOT23 3-pin and 8-pin examples.

Figure 1. Graphic showing 0.5 mm pitch SOT23 3-pin and 8-pin examples.

# 0.5 mm Pitch SOT23 Fanout Examples

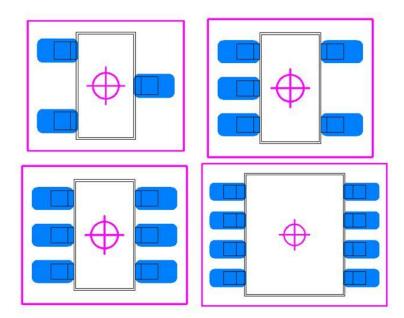

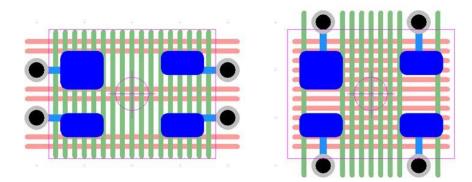

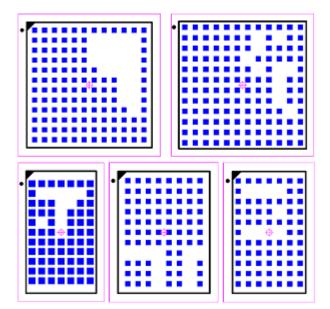

Figure 2 illustrates four different 0.5mm pitch 3-pin SOT23 land pattern via fanout techniques. The SOT23 parts are placed on a 0.5 mm grid system and all the vias snap to a 1.0 mm grid.

There are two 0.1 mm trace/space technology on all layers.

Via land size is 0.5 mm, hole size is 0.25 mm and plane anti-pad is 0.7mm

Figure 2. Four different 0.5mm pitch 3-pin SOT23 land pattern via fanout techniques.

# 0.5 Mm Pitch SOT23 Fanout Examples

Figure 3 illustrates four different 0.5mm pitch 8-pin SOT23 land pattern via fanout techniques. The SOT23 parts are placed on a 0.5 mm grid system and all the vias snap to a 1.0 mm grid. This allows two 0.1 mm trace/space technology on all layers.

Figure 3. Four different 0.5mm pitch 8-pin SOT23 land pattern via fanout techniques.

Figure 4 illustrates 0.65 mm pitch SOT23 3-, 5-, 6- and 8-pin examples.

# 0.65 mm Pitch SOT23 Fanout Examples

Figure 5 illustrates five different 0.65mm pitch 3-, 5-, 6- and 8-pin SOT23 land pattern via fanout techniques. The SOT23 parts are placed on a 0.5 mm grid system and all the vias snap to a 1.0 mm grid. This allows two 0.1 mm trace/space technology on all layers with 0.5 mm via land.

# Figure 5.

Figure 6 illustrates 0.95 mm pitch SOT23 3-, 5-, 6- and 8-pin examples.

# Figure 6.

# 0.95 mm Pitch SOT23 Fanout Examples

Figure 7 illustrates seven different 0.95mm pitch 3-, 5-, 6- and 8-pin SOT23 land pattern via fanout techniques. The SOT23 parts are placed on a 0.5 mm grid system and all the vias snap to a 1.0 mm grid. This allows two 0.1 mm trace/space technology on all layers.

# Figure 7. Seven different 0.95mm pitch 3-, 5-, 6- and 8-pin SOT23 land pattern via fanout techniques.

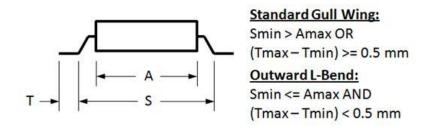

The SOT component family uses a gull wing component lead. All gull wing leaded components have four different sets of land pattern rules. These examples are for the "Nominal Environment".

Pin pitch less than 0.625mm (side goal is -0.02 mm) considered "fine pitch"

Pin pitch greater than 0.625 mm (side goal is 0.03 mm)

Outward flat ribbon with pin pitch less than 0.625mm (heel goal is 0.15 mm and side goal is -0.02 mm)

Outward flat ribbon with pin pitch greater than 0.625mm (heel goal is 0.15 mm and side goal is 0.03 mm)

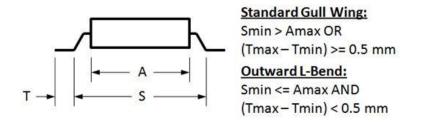

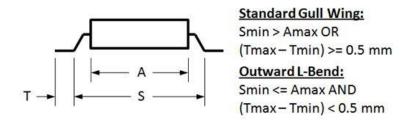

The formula that calculates the difference between gull wing and outward flat ribbon (mini gull wing) is shown in Figure 8.

# Figure 8. Formula that calculates the difference between gull wing and outward flat ribbon.

We already discussed chip and molded body assembly outlines and ref des in the last column. It's important to note that the lands (pads) do not get added to the assembly drawing layer for small parts. The two most important things on the assembly drawing are the Ref Des and Component Outline. If the

part is too small and the lands interfere with the Ref Des, then do not add the top assembly lands to the padstack. However, if the lands do not interfere with the Ref Des then we should add the top assembly lands to the padstack.

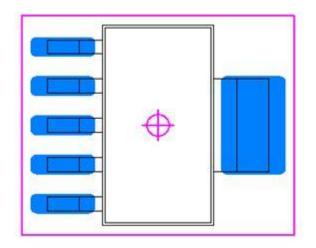

Here are some of the various assembly outlines for the 0.95 mm pitch SOT23 component family. See Figure 9 for the 3-, 5- and 6-pin versions of the assembly outline, Ref Des, polarity marker for pin 1 location and lands (pads).

Figure 9. Silkscreen outlines for the various SOT component families.

There are a number of silkscreen outlines for the various SOT component families; Figure 9 illustrates several of them. See Figure 10 for the SOT23 silkscreen outline, polarity marker and 0.5 mm post-assembly inspection dot for pin 1 location and lands (pads). In this case the silkscreen outline is too narrow for an adequate polarity marker inside the outline, so the post assembly inspection dot for pin 1 will have to be sufficient.

Figure 10. Silkscreen outline, polarity marker and 0.5 mm post-assembly inspection dot.

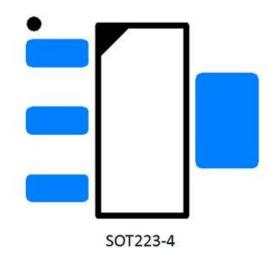

# **SOT223 Components**

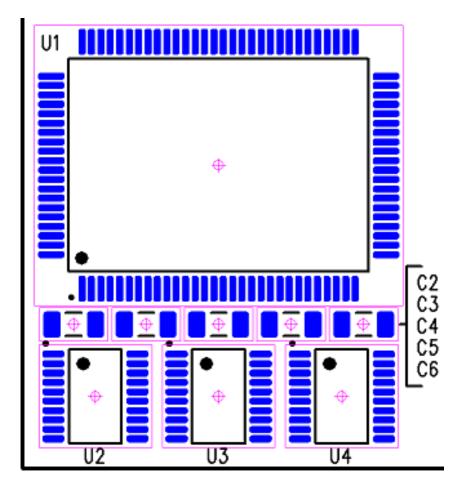

The SOT223 is the second-most popular part in the small outline transistor (SOT) component families. The SOT223 comprises 4-, 5- and 6-pin variations as well as three popular pin pitches, which include 1.27 mm, 1.50 mm and 2.30 mm pitch. Figure 1 shows the 6-pin 1.27 mm pitch SOT223 land pattern. The particular land pattern shown is portrayed in the Nominal Environment.

# Figure 1: SOT 223 with 1.27 mm pitch (Nominal Environment).

Figure 2 shows the 6-pin 1.27 mm pitch SOT223 land pattern via fanout. This fanout uses a power via with a 1.00 mm land and a 0.50 mm hole snapped to a 1.00 mm grid. The signal trace/space rules are for this layout are 0.10 mm.

Figure 2: 6-pin, 1.27 mm fanout.

Figure 3 shows the 5-pin 1.50 mm pitch SOT223 land pattern.

# Figure 3. 5-pin 1.50 mm pitch land pattern.

Figure 4 shows the 5-pin 1.50 mm pitch SOT223 land pattern via fanout. This layout also uses a power via with a 1.00 mm land and a 0.50 mm hole snapped to a 1.00 mm grid. The trace/space rules are also 0.10 mm.

Figure 4: 5-pin, 1.50 mm pitch fanout.

Figure 5 shows the 4-pin 2.30 mm pitch SOT223 land pattern. Figure 6 shows the 4-pin 2.3 mm pitch SOT223 land pattern via fanout using the same power and trace/space rules as the previous examples.

Figure 5: 4-pin, 2.30 mm pitch land pattern.

Figure 6: 4-pin, 2.30 mm pitch fanout.

# **Component Leads**

The SOT223 component family uses a "gull wing" component lead. All gull wing leaded components have four different sets of land pattern rules. These example rules are for the Nominal Environment:

Pin pitch less than 0.625 mm (side goal is -0.02 mm) considered "fine pitch."

Pin pitch greater than 0.625 mm (side goal is 0.03 mm).

Outward flat ribbon with pin pitch less than 0.625 mm (heel goal is 0.15 mm and side goal is -0.02 mm).

Outward flat ribbon with pin pitch greater than 0.625 mm (heel goal is 0.15 mm and side goal is 0.03 mm).

The formula that calculates the difference between gull wing and outward flat ribbon is shown in Figure 7.

# Figure 7: Dimensions for standard gull wing vs. outward L-bend.

We've already discussed chip and molded body assembly outlines and ref des. It's important to note that the lands (pads) do not get added to the assembly drawing layer for small parts. The two most important items on the assembly drawing are the ref des and component outline. If the part is too small and the lands interfere with the ref des, then do not add the top assembly lands to the padstack. However, if the lands do not interfere with the ref des, then add the top assembly lands to the padstack.

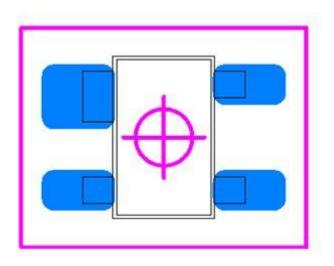

Here are some of the various assembly outlines for the SOT223 component family. See Figure 8 for the 4-, 5- and 6-pin versions of the assembly outline, ref des, and polarity marker for pin 1 location and lands (pads).

# Figure 8: Assembly outlines for 4-, 5- and 6-pin SOT223.

Figure 9 illustrates some of the various silkscreen outlines for the SOT component families, including the SOT223 version of the silkscreen outline, polarity marker and 0.50 mm post-assembly inspection dot for pin 1 location and lands (pads).

Figure 9: 4-pin example silkscreen outline.

# SOT143 and SOT343 Components

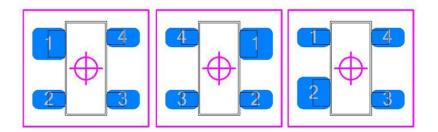

After the SOT223, the next-most popular small outline transistors (SOT) component families are the SOT143 and SOT343. Both families have four pins, with a larger Pin 1. The pin pitch is 1.90 mm.

#### SOT143 Family

There are three different pin configurations for the SOT143 package: Pin 1 is wide pin on upper left, Pin 1 is wide pin on upper right (reverse pin order), and the third has Pin 2 as a wide pin on lower left (custom). Figure 1 illustrates all three of these patterns.

Figure 1: The three pin 1 configurations for the SOT143.

Figure 2 shows the 4-pin 1.90 mm pitch SOT143 land pattern via fanout using a via with a 0.50 mm land and a 0.25 mm hole snapped to a 1.00 mm grid. The trace/space rules are 0.10 mm and the routing grid is 0.10 mm.

Figure 2: SOT143 via fanout.

# SOT343 Family

The SOT343 is the next most popular component family. This family of components also has four pins, with Pin 1 always in the upper left quadrant. Pin 1 is also wider than the other three pins. See Figure 3.

Figure 3: Land pattern for the SOT343 family.

Figure 4 shows the 4-pin 1.30 mm pitch SOT343 land pattern via fanout using a via with a 0.50 mm land and a 0.25 mm hole snapped to a 1.00 mm grid. Like the SOT143, the trace/space rules are 0.10 mm and the routing grid is 0.10 mm. The via fanout direction depends on which layer you need more routing channels.

Figure 4: SOT343 fanout.

# **Component Leads**

Both the SOT143 and SOT343 component families use a gull-wing component lead. All gull-wing leaded components have four different sets of land pattern rules. These rule examples are for the "Nominal Environment."

Pin pitch less than 0.625 mm (side goal is -0.02 mm) considered "fine pitch."

Pin pitch greater than 0.625 mm (side goal is 0.03 mm).

Outward flat ribbon with pin pitch less than 0.625 mm (heel goal is 0.15 mm and side goal is -0.02 mm).

Outward flat ribbon with pin pitch greater than 0.625 mm (heel goal is 0.15 mm and side goal is 0.03 mm).

The formula that calculates the difference between gull-wing and outward flat ribbon (mini gull-wing) is shown in Figure 5.

#### Figure 5: Dimensions for standard gull-wing and outward L-bend leads.

We already discussed chip and molded body assembly outlines and ref des. It's important to note that the lands (pads) do not get added to the assembly drawing layer for small parts. The two most important aspects of the assembly drawing are the ref des and component outline. If the part is too small and the lands interfere with the ref des, then do not add the top assembly lands to the padstack. However, if the lands do not interfere with the ref des, then we should add the top assembly lands to the padstack.

Figure 6 illustrates some of the assembly outlines for the SOT143 component family showing both standard and reverse pin versions of the assembly outline, ref des, polarity marker for pin 1 location and lands (pads).

Figure 6: Assembly outlines for SOT143.

Figure 7 illustrates some of the various silkscreen outlines for the SOT component families. These include the SOT143 version of the silkscreen outline, polarity marker and 0.5 mm post-assembly inspection dot for pin 1 location and lands (pads).

Figure 7: Silkscreen for SOT143 components.

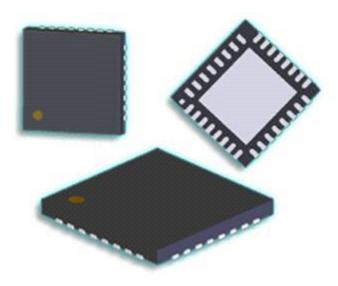

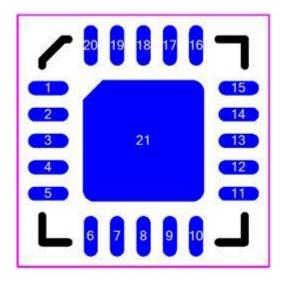

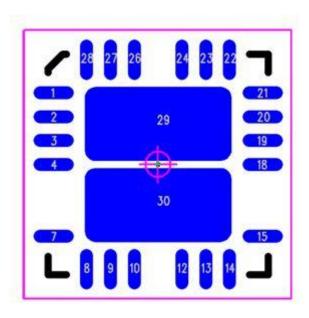

# **BGA Components**

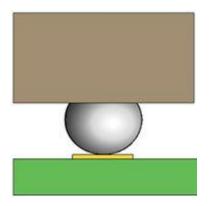

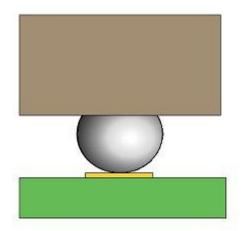

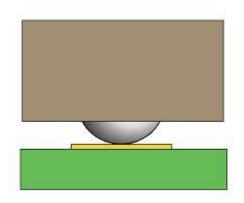

The ball grid array, commonly known as the BGA, has been around since the 1980s. The pin pitch began at 1.50 mm and then quickly went to 1.27 mm (50 mils), where it held steady for about 15 years. Then in the late 1990s, the 1.00 mm pitch BGA was introduced. Every few years since then, the pin pitch has dropped. Today 0.40 mm pitch BGAs are in every cell phone and 0.30 mm pitch BGAs are the next generation. Figure 1 shows the lead type for this component family.

# Figure 1. BGA leads — a lead ball collapsed against the PCB land.

Ball grid array components can have one of two types of ball leads:

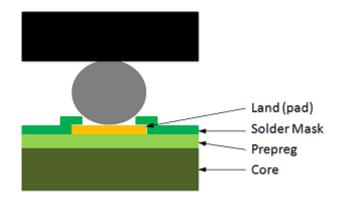

Non-collapsing - this is normally employed for 0.50 mm pitch and smaller BGAs, where the land (pad) is larger than the ball to allow for via-in-pad technology and to provide an adequate annular ring. The solder mask can be the same size as the land with non-collapsing balls. In some cases, the land for fine pitch BGAs is solder-mask defined where the solder mask encroaches slightly over the land. This provides protection for any trace routing between the lands but the most significant benefit is to help secure the land to the PCB. During cell phone "drop testing", the BGA solder joint normally holds better than the land to the Prepreg. i.e.: drop tests prove that the non-solder-mask land will rip from the PCB before the solder joint breaks. So the solder-mask defined land is secured better to the PCB for drop testing.

Collapsing - this is normally 0.65 mm pitch and larger, where the land (pad) is smaller than the ball size to allow the ball to collapse around the sides of the land. This requires a non-solder-mask-defined land where the solder mask must be larger than the land.

Figure 2 illustrates examples of non-collapsing and collapsing BGA balls.

Figure 2. Non-collapsing ball (left) and collapsing ball (right) BGAs, highly magnified.

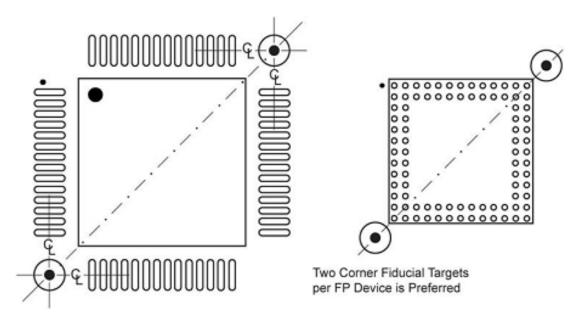

The BGA land (pad) size is determined by the ball size as seen below in Table 1, from the IPC-7351B land pattern standard. Notice the correlation between the "reduction" and the "land pattern density level." The three density levels change the land size reduction percentage, but they also determine the placement courtyard excess (See Table 3).

| Nominal<br>Ball<br>Diameter | Reduction        | Land<br>Pattern<br>Density<br>Level | Nominal<br>Land<br>Diameter | Land<br>Variation  |

|-----------------------------|------------------|-------------------------------------|-----------------------------|--------------------|

| 0.75                        | 25%              | A                                   | 0.55                        | 0.60 - 0.50        |

| 0.65                        | 25%              | Α                                   | 0.50                        | <b>0.55</b> - 0.45 |

| 0.60                        | <mark>25%</mark> | Α                                   | 0.45                        | 0.50 - 0.40        |

| 0.55                        | 25%              | А                                   | 0.40                        | 0.45 - 0.35        |

| 0.50                        | 20%              | В                                   | 0.40                        | <b>0.45</b> - 0.35 |

| 0.45                        | 20%              | В                                   | 0.35                        | 0.40 - 0.30        |

| 0.40                        | 20%              | В                                   | 0.30                        | <b>0.35</b> - 0.25 |

| 0.35                        | 20%              | В                                   | 0.30                        | 0.35 - 0.25        |

| 0.30                        | 20%              | В                                   | 0.25                        | 0.25 - 0.20        |

| 0.25                        | 20%              | В                                   | 0.20                        | <b>0.20</b> - 0.17 |

| 0.20                        | 15%              | C                                   | 0.17                        | 0.20 - 0.14        |

| 0.17                        | 15%              | С                                   | 0.15                        | <b>0.18</b> - 0.12 |

| 0.15                        | 15%              | С                                   | 0.13                        | 0.15 - 0.10        |

# Table 1. Land approximation (mm) for collapsible solder balls.

Note: The IPC-7351B LP Calculator uses this chart for calculations

It is very important to note that IPC prefers the Maximum Material Condition for all BGA Land sizes; IPC does not use the Nominal Land Diameter, but instead uses the Maximum Land Variation Diameter (notice the bold numbers in the chart's land variation column). The standard ball sizes are in 0.05 mm increments until the pin pitch hits 0.50 mm or less. However, even though the world standards organizations try to keep BGA balls sizes in 0.05 mm increments, component manufacturers sometimes do not adhere to the standard and create BGA ball sizes in 0.01 mm increments.

But I have never seen a BGA ball size less than a 0.01 mm increment. Also, the BGA pin pitches are in 0.05 mm increments. As a result, the BGA land (pad) sizes are in 0.05 mm increments, including the via fanout padstacks and hole sizes.

IPC-7351B features a three-tiered BGA formula for placement courtyard excess that uses the BGA ball size to calculate an adequate placement courtyard for BGA rework tools. If the BGA has a large ball size, larger rework equipment is necessary to unsolder the increased solder volume.

With a small ball size, the placement courtyard can be smaller because less heat is then required to unsolder the BGA component for rework. However, the end-user may not plan to rework the BGA if it fails. In that case, there is no need to have a robust placement courtyard, but a recommended minimum placement courtyard excess is 0.5 mm.

#### **Non-Collapsing Ball BGA Components**

| Nominal<br>Ball<br>Diameter | Increase | Nominal<br>Land<br>Diameter | Land<br>Variation |

|-----------------------------|----------|-----------------------------|-------------------|

| 0.75                        | 15%      | 0.85                        | 0.90 - 0.80       |

| 0.65                        | 15%      | 0.75                        | 0.80 - 0.70       |

| 0.60                        | 15%      | 0.70                        | 0.75 - 0.65       |

| 0.55                        | 15%      | 0.65                        | 0.70 - 0.60       |

| 0.50                        | 10%      | 0.55                        | 0.60 - 0.50       |

| 0.45                        | 10%      | 0.50                        | 0.55 - 0.45       |

| 0.40                        | 10%      | 0.45                        | 0.50 - 0.40       |

| 0.35                        | 10%      | 0.40                        | 0.45 - 0.35       |

| 0.30                        | 10%      | 0.35                        | 0.40 - 0.30       |

| 0.25                        | 10%      | 0.30                        | 0.35 - 0.25       |

| 0.20                        | 5%       | 0.21                        | 0.26 - 0.16       |

| 0.17                        | 5%       | 0.18                        | 0.22 - 0.13       |

| 0.15                        | 5%       | 0.16                        | 0.21 - 0.11       |

Table 2 shows land size calculations for non-collapsing BGA balls.

#### Table 2. Non-collapsing BGA ball land calculations.

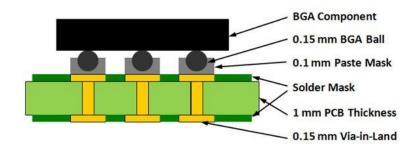

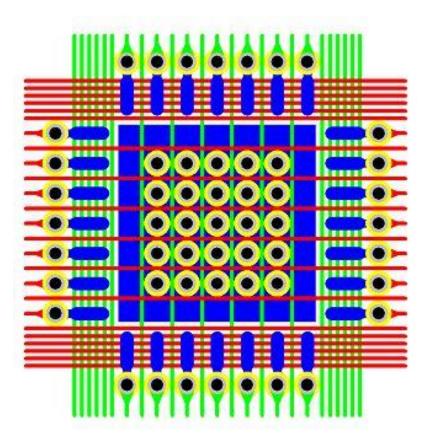

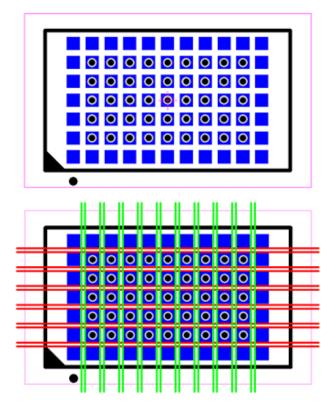

Figure 3 is a 0.50 pitch non-collapsing BGA ball. Instead of shrinking, the non-collapsing land size gets larger to handle the solder volume that creates the solder joint. This technology is new to the electronics industry and was created as a solution for lead-free BGA balls and via-in-pad technology as a routing solution for fine pitch BGA components.

Figure 3. Non-collapsing 0.5 mm pitch BGA.

| Via-in-Land Technology  | Trace/Space & Grid Data  |  |  |

|-------------------------|--------------------------|--|--|

| BGA Ball Size: 0.15     | Trace Width: 0.075       |  |  |

| BGA Land Dia: 0.275     | Trace/Trace Space: 0.075 |  |  |

| Hole Size: 0.15         | Trace/Via Space: 0.075   |  |  |

| Thermal Relief Required | Trace/BGA Land: 0.075    |  |  |

| Plane Clearance: 0.425  | Routing Grid: 0.05       |  |  |

| Solder Mask: 1:1 scale  | Part Place Grid: 1       |  |  |

IPC-7351A has a three-tiered BGA formula for placement courtyards that uses the BGA ball size to calculate an adequate placement courtyard for BGA rework tools.

If the BGA has a large ball size, larger rework equipment is necessary to unsolder the large solder volume. With a small ball size, the placement courtyard can be smaller as less heat is then required to unsolder the BGA component for rework. However, the end user may not plan to rework the BGA if it fails. In that case, there is no need to have a robust placement courtyard.

Table 3 below represents the three-tiered scenario and the different placement courtyard excess size determination.

| Lead Part              | Most Density<br>Level A                                                          | Nominal<br>Density Level B | Least Density<br>Level C |  |

|------------------------|----------------------------------------------------------------------------------|----------------------------|--------------------------|--|

| Collapsing Ball        | 25% Reduction                                                                    | 20% Reduction              | 15% Reduction            |  |

| Non-collapsing<br>Ball | 15% Reduction                                                                    | 10% Reduction              | 5% Reduction             |  |

| Courtyard<br>Excess    | 2.00                                                                             | 1.00                       | 0.50                     |  |

| Round-off Factor       | Round off to the nearest two place 0.05 decimal, i.e.:<br>1.00, 1.05, 1.10, 1.15 |                            |                          |  |

Table 3. BGA density levels for placement courtyard size determination.

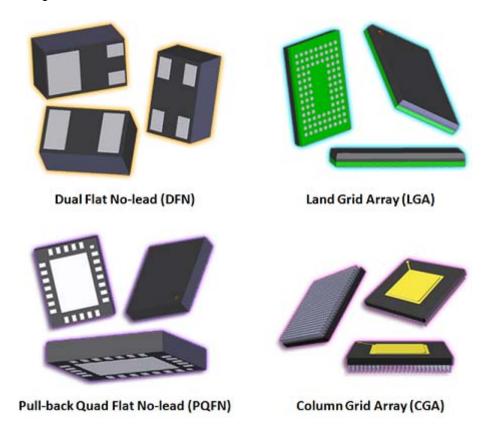

# **SMD Bottom and Flat Lead Forms**

Before we go deeper into the various component families, we need to clarify the component lead forms of today's component packaging technology: What is going to be eventually phased out, what is new and why. This is Part 1 of 2 columns on component lead forms. Part 2 will cover side and bent leads.

The pin (component lead) pitch and the overall body height are continually shrinking. This is why the SSOP and TSOP land pattern names have to be dropped from the standard. In this nomenclature, S = Shrink for fine pitch and T = Thin for low profile height.

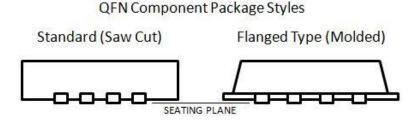

If these two values are constantly changing, then where is the line drawn? Whose part is thin or fine pitch, and by what measure? The gull-wing lead has hit the limit at 0.40 mm pitch. Most assembly shops will try to convince you to swap that part out of your design for a larger pin pitch. However, no-lead SON and QFN lead styles are being produced and manufactured at 0.40 mm pitch with no problems. The finer-pitch parts have more I/Os and a smaller footprint with a much lower profile than J-lead or gull-wing packages, so it's obvious that the component industry is going to be no-lead or bottom-only flat-lead or side-lead packages.

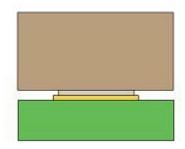

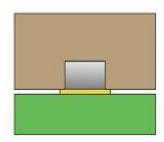

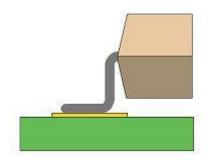

Let's review the bottom-only and flat-component lead forms. The BGA has been around since the 1980s but the pin pitch started out with 1.50 mm and then quickly went to 1.27 mm (50 mils) for about 15 years. Then in the late 1990s, the 1.00 mm pitch BGA was introduced and every couple years a smaller pin pitch was introduced. Today 0.4 mm pitch BGAs are in every cell phone and 0.3 mm pitch BGAs are the next generation. See Figure 1.

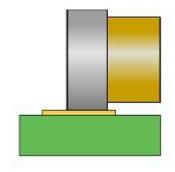

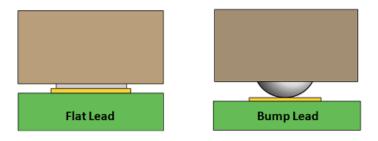

Figure 1. BGA ball-to-land illustration.

For more information about BGAs, read my white paper "Metric Pitch BGA and Micro BGA Routing Solutions."

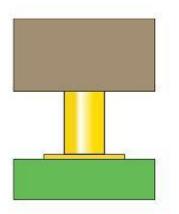

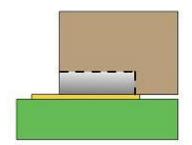

The next lead form in the bottom-only category is the "bump" lead. This is widely used in a package called land grid array or LGA. The land (pad) size can be the same as the maximum bump lead diameter. Via-in-pad technology can be much more forgiving with the bump lead than BGA voids due to a dimple in the land after the plug and plate process. This lead form is also highly compatible with lead-free solder. See Figure 2.

# Figure 2.

The next grid array lead form is the bottom flat, which is also used in LGA component packages. Linear Technologies is the leading provider of bottom flat lead LGA packages. This lead form is also highly compatible with lead-free solder alloys as there is no requirement for wetting (flow) properties in the solder.

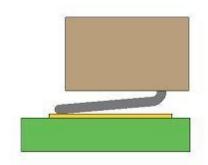

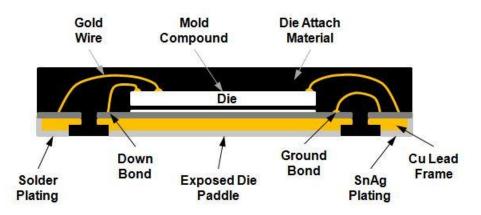

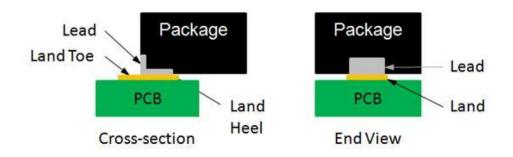

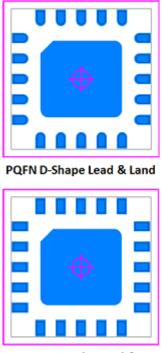

The other flat no-lead is referred to as a "pull-back" or "bottom-only" lead. We can also categorize the pull-back lead small outline no-lead (SON) and quad flat no-lead (QFN) component packages with this solder joint goal, as a slight periphery land is required to allow the solder to move from under the lead to the periphery to surround the protruding lead for a solid solder joint.

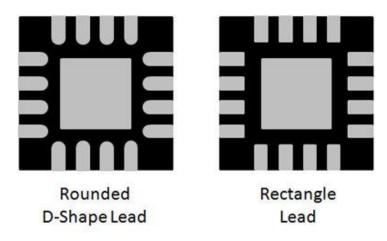

The solder joint goal is a periphery land around the terminal. Pull-back or bottom-only leads come in three lead shapes:

D-Shape (or vullet in some CAD tools)

Square

Rectangle

This lead style has the same solder joint goals as the bottom-only "bump" LGA lead. See Figure 3.

# Figure 3.

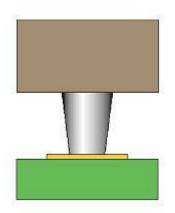

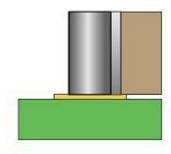

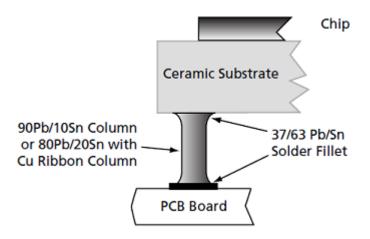

The next grid array component lead is the "column." Actel and Xilinx are the leading manufacturers of this lead style. You will not find any pin pitches smaller than 1.00 mm for the column lead. The land must be slightly larger than the column to form a good solder joint. See Figure 4.

# Figure 4.

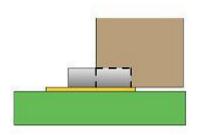

The last SMT grid array is the newest lead form in the industry: the "pillar column." Recently introduced by Actel, this component lead has much promise for an improved solder joint. But time will tell how long this one will last. See Figure 5.

# Figure 5.

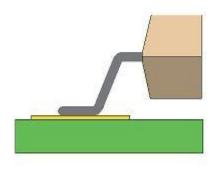

Flat lead components are coming on strong. These are the SODFL (Small Outline Diode Flat Lead) 2leaded components and the SOTFL (Small Outline Transistor Flat Lead) packages that come in 3-, 5-, 6and 8-lead components. Both of these component families are the direct replacement for the gull-wing lead SOD and SOT-23 packages. See Figure 6.

Figure 6.

Flat no-lead is used in the SON (Small Outline No-lead) with terminals on two sides and QFN (Quad Flat No-lead) with leads on four sides. The most common SON & QFN today is the "edge" lead, where the component lead starts under the component and goes out to the component body edge. This solder joint goal requires a toe, heel and side solder fillet where the toe joint is visible for inspection. See Figure 7.

# Figure 7

The flat thermal lead comes in a DPAK where the signal pins and gull-wing and thermal lead are flat. The flat thermal lead is also used as the heat sink for SON, QFN, SOP and QFP packages. It is usually embedded in the plastic component body and therefore the solder joint goals are usually 1:1 scale for the maximum component lead size and land size. See Figure 8.

# Figure 8

The last component lead form in the list is the "underbody outward L." This lead form is used for aluminum electrolytic capacitors and two-pin SMD crystals. This lead form has two different solder joint goals that are based on the component height. Once the component height exceeds 10 mm, the solder joint goals have to be more robust. See Figure 9.

# **SMD Side and Bent Lead Forms**

Recall in last week's column, the pin (component lead) pitch and the overall body height are continually shrinking. This is why the SSOP and TSOP land pattern names have to be dropped from the standard: S = Shrink for fine pitch and T = Thin for low profile height. If these two values are constantly changing, where is the line drawn? Whose part is thin or fine pitch and by what measure? The gull-wing lead has hit the wall at 0.4 mm pitch.

Most assembly shops will try to convince you to swap that part out of your design for a larger pin pitch; however, no-lead SON and QFN lead styles are being produced and manufactured at 0.4 mm pitch with no problems. The finer-pitch parts have more I/Os and a smaller footprint with a much lower profile than J-lead or gull-wing packages, so it's obvious that the component industry is going to be no-lead or bottom only flat lead or side lead packages.

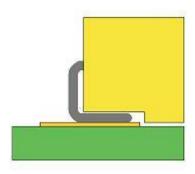

The "corner concave" lead form is primarily used for the oscillator component family. It's perfect for oscillators because it only has the four leads that are necessary for the standard oscillator requirements. See Figure 1.

# Figure 1.

The "cylindrical end cap" goes with the metal electrode lead face (MELF) component family for resistors and diodes. I just can't figure out why the industry still produces round components, but engineers continue to design them into their schematics. In some cases these components can easily roll off the workbench or circuit board before they have been soldered into place because of their cylindrical shape and small size. As such, there is a joke that suggests an alternate meaning for the acronym MELF: "Most End up Lying on Floor."

Mostly, this happens if the mechanical pressure of the SMD placer nozzle is too low. If the MELF resistors are placed into the solder paste with enough pressure this problem can be minimized. But be careful if SOD-80 glass diodes are used; those types are different compared to MELF resistors and the mechanical robustness is limited. See Figure 2.

# Figure 2.

Every PCB designer is familiar with the gull-wing lead (See Figure 3), but it has two separate rule sets that are defined by the pin pitch:

Less than 0.625 mm pitch (fine pitch)

Greater than 0.625 mm pitch

These component families include:

Ceramic flat package (CFP)

Ceramic quad flat package (CQFP)

Quad flat pack (QFP)

Small outline diode (SOD)

Small outline package (SOP)

Small outline transistor (SOT)

Transistor outline (TO)

Figure 3.

The "inward flat ribbon L" is used for the molded body component family. This includes polarized and nonpolarized capacitors, inductors, resistors and LEDs. The most popular is the tantalum capacitor. See Figure 4.

# Figure 4.

The "J-lead" is one of the original SMT leads that became popular with the PLCC (plastic leaded chip carrier) and then the SOJ (small outline J-lead). This lead form was very popular because the leads were stable and easy to manually solder. And the solder joint was easy to inspect. However, with the advent of high speed technology, lead-free solder, low profile fine pitch component packages, this lead form will be one of the first SMT leads to become obsolete. See Figure 5.

# Figure 5.

The "outward flat ribbon L" lead is used to reduce the footprint size of SOT and SOP components. It's similar to a gull wing lead, but the lead bends downward immediately coming out of the component body and then is bent flat. The flat lead is very compatible with lead-free solder alloys and takes up less PCB real-estate. Since there is no heel and these components are so "low profile," the land is usually trimmed at the nominal component body. If the land (pad) protrudes under the component body, it will end up with solder on the bottom of the component during reflow. See Figure 6.

The outward L lead also has two separate rule sets that are defined by the pin pitch:

Less than 0.625 mm pitch (fine pitch)

Greater than 0.625 mm pitch

# Figure 6.

The "rectangular end cap" is used for discrete resistors, capacitors, inductors and LEDs. This lead type is by far the most popular due to the component count. The rectangular end cap lead form makes up 80-90% of the total part quantity of the average PCB. These components are easy to manually solder and easy to rework if necessary. However, the new DFN (dual flat no-lead) component with bottom only terminations is better for lead-free solder and part placement density. See Figure 7.

Figure 7.

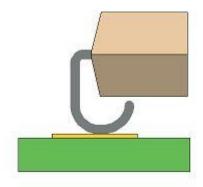

The "side lead" comes in 3 different lead styles (See Figures 8, 9 & 10):

Concave

Convex

Flat

The side lead is on the outside perimeter of the component body and normally runs from the bottom to the top of the component. It is used widely for chip arrays and LCC (leadless chip carriers) and has 2 different sets of solder joint goals depending on the lead pitch:

Pitch is less than or equal to 1 mm

Pitch is greater than 1 mm

Figure 8. Concave side lead.

Figure 9. Flat side lead.

Figure 10. Convex side lead.

Now we have covered all the component lead forms. Next week, we'll dive into the various component families and relate their lead forms back to this post. It's going to be interesting to find out what new component lead will be invented by a component manufacturer in the years to come, but when they do, the IPC-7351 land pattern committee will be there to develop the optimized solder joint goal chart.

# **Placement Courtyards**

The IPC-7351B standard focuses on five two major aspects of the CAD library:

- 1. Land (pad) size and spacing calculations

- 2. Placement courtyard excess boundary

- 3. Land pattern naming convention

- 4. Zero component orientation

- 5. Padstack naming convention

All of the other aspects of the CAD library section such as silkscreen and assembly outlines, polarity markings, reference designators, centroid marking, etc. are considered user-definable drafting items. This includes all of the rules that pertain to these items such as line widths, silkscreen to land spacing, polarity sizes, reference designator height, etc. They are not part of the IPC-7351B standard.

The placement courtyard boundary *is* defined in the IPC-7351B standard, but the line width used to create the closed polygon outline shape is user-definable. There are industry recommendations, like the IPC-2610 series for fabrication and assembly documentation. The IPC LP Calculator uses 0.05 mm as the default line width. The default solder mask and paste mask values are mentioned in the IPC-7351B as to be 1:1 scale of the land size, but this is only a recommendation.

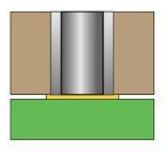

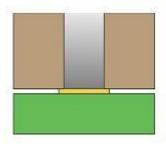

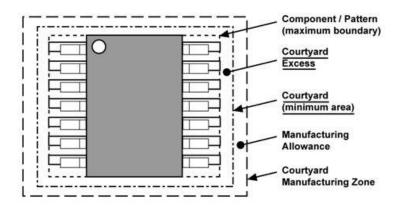

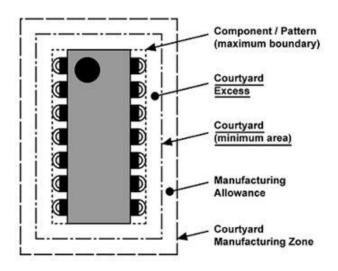

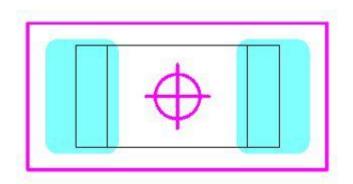

See courtyard determination in Figures 1 and 2 below to see the three outlines defined by IPC-7351B as:

Maximum component boundary

Minimum placement courtyard

Courtyard manufacturing zone

Figure 1. Plated through-hole courtyard excess determination.

#### Figure 2. Plated through-hole courtyard excess determination.

Here are the IPC-7351B standard spacing rules from the maximum component boundary to the minimum placement courtyard excess:

Least environment = 0.1 mm

Nominal environment = 0.25 mm

Most environment = 0.5 mm

There are different placement courtyard spacing rules for grid array packages based on ball size:

Ball size above 0.50 mm = 2 mm

Ball size between 0.50 mm & 0.25 mm = 1 mm

Ball size below 0.25 mm = 0.5 mm

One of the key aspects of the placement courtyard is that it allows room for rework. In the case of the BGAs, the larger the ball size, the larger the heat nozzles and removal equipment used for getting around and under the component to unsolder the contacts.

An important note to make here is that if you have no intentions of ever reworking (removing and replacing) a BGA component, the 2 mm placement courtyard is not necessary and a 0.5 mm courtyard excess is okay. This also is relevant to the "most environment" where the minimum courtyard excess is 0.5 mm on all SMT land patterns, i.e., the military and medical instrument industry might use the "most environment" and require "Class 3" *High Reliability Electronic Products* where continued high-performance is critical and product downtime cannot be tolerated. The Class 3 fabrication is very expensive and if a component on the PCB fails, rework becomes necessary to reduce cost. Rework requires additional land pattern placement courtyard excess to allow adequate space for rework equipment.

Alternatively, the "least environment" for high-density PCB layout, such as handheld devices, has a courtyard excess of 0.1 mm with no room for rework equipment. So, if a component fails in your cellular phone, it will not be sent back to the shop for rework, but instead, it will be discarded.

The placement courtyards can be placed next to each other so the outline overlaps; however, you need to discuss this with your assembly shop if they require an additional manufacturing zone for their process. The placement courtyard round-off snap grid is 0.5 mm. The question of "why don't you place the silkscreen outline outside the land pattern boundary" is a FAQ and this is the answer: "It is important that all silkscreen outline data be located inside the placement courtyard."

This rule includes the post-assembly inspection dot, which sometimes gets partially placed outside the placement courtyard. This is why, in the upcoming IPC-2614 for board fabrication documentation and drafting standards, the "post-assembly inspection *dot*" will become the "post-assembly inspection *line*" and it will look like this to keep them inside the placement courtyard outline. See Figure 3.

Also, the line in most cases has higher visibility on the assembled PCB. The post-assembly inspection marker is used for post-assembly QC for possible component inverted (incorrect) assembly orientation. The polarity marker on the component should align with the post assembly Inspection silkscreen marking.

Figure 3. Post-assembly inspection lines inside placement courtyard.

The placement courtyard or courtyard excess is the smallest area that provides a minimum electrical and mechanical clearance of the maximum extremities of the land pattern and/or the component body. However, it is the responsibility of the user to verify the land patterns used for achieving an undisturbed mounting process including testing and an ensured reliability for the product stress conditions in use.

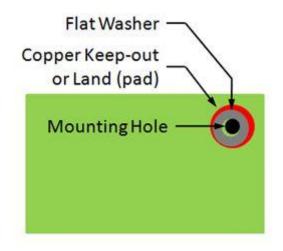

For many through-hole parts and connectors, the placement courtyard will follow the contour of the component body outline and land pattern. See Figure 4.

Figure 4. PTH resister courtyard.

Most enterprise CAD tools – for instance, Mentor Graphics Expedition Enterprise – have a different DRC checking feature that the user can define the component type to component type spacing rules. In this case, the placement courtyard excess should be turned off and the placement courtyard would be identical to the maximum component boundary. The maximum component boundary is a combination of whichever land pattern features, land (pad) or component body which protrude the most from the center.

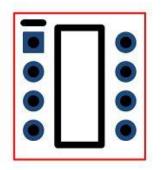

# Figure 5. Enterprise CAD tool placement courtyard.

The Enterprise CAD tool placement courtyard is not defined in the IPC-7351 standard. This concept is based on the Enterprise CAD tools ability to determine various components body to body spacing that are user-definable rules within the CAD tool options.

# **Land Calculation**

IPC-7351B for SMT technology defines the rules for creating optimized land pattern CAD library parts using a three-tier system: Least (high density), Nominal (controlled environment) and Most (ruggedized and shock resistant). Many PCB designers and CAD librarians have heard about the IPC-7351B standard, but few people know how it works. The IPC LP Calculator has made life easy for the PCB design industry by automatically generating accurate land pattern data derived from component dimensions.

# Land (Pad) Size and Location

These 7 factors are used to calculate the optimum land size:

Component Body Tolerance

Component Terminal Tolerance

**Fabrication Tolerance**

Placement Tolerance

Land Size Round-off

Land Spacing Round-off

Solder Joint Goals for Toe, Heel and Side

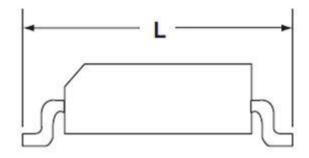

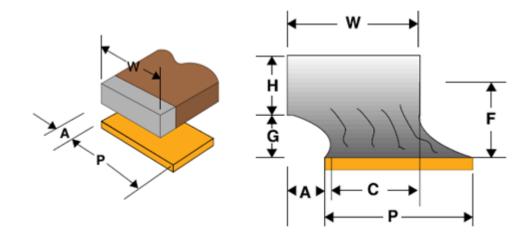

IPC-7351 identifies two component body dimensions: "A" (body width) and "B" (body length). The one SMT *Component Body Tolerance* that affects the land pattern is the minimum and maximum sizes of the component "lead span" (the dimension from lead tip to lead tip) dimension "L." This varies for different component packages. For gull wing or J-lead, it's the distance from outside lead tip to tip. For chip resistors or capacitors, it's the full tolerance of the overall body. The picture below represents the "L" dimension of a gull-wing lead component. See Figure 1.

#### Figure 1. Lead span.

The **Component Terminal Tolerance** is the size of the metalized area that actually touches the land area. IPC refers to this as the component footprint. The footprint must compensate for the minimum and maximum lead tolerance for the calculation of an optimized land size. The component lead footprint is then synchronized with the appropriate land pattern. See Figure 2.

Figure 2. Terminal tolerance.

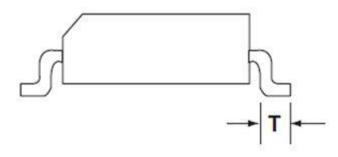

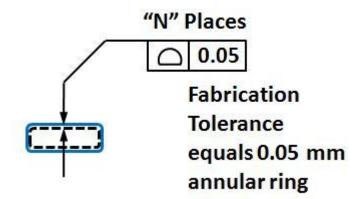

The *Fabrication (Manufacturing) Tolerance* compensates for the fabrication allowance for etchback. By adding a fabrication tolerance, we calculate the land area that we need after the fabrication etching process. The IPC-7351 fabrication tolerance is 0.05mm. See Figure 3.

Figure 3. Fabrication tolerance.

The *Placement (Assembly) Tolerance* compensates for the pick-and-place machine accuracy. When parts are manually placed or machine placed, there is a small margin of placement accuracy that must be accounted for. The IPC-7351 assembly tolerance is 0.05mm.

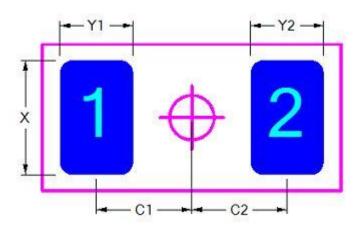

*Land Place (Spacing) Round-off* relates to the land center to land center spacing. The goal in the IPC-7351 is to place all lands on a 0.05mm grid, so the space between the land span is rounded to 0.1mm increments so that the distance from the center of the land pattern to the center of the land is in 0.05mm increments. This plays a critical role in trace routing to achieve the highest packing density and cleanest routing results. In this example of a common chip component in Figure 4, the land snap grid is 0.05 mm from the center of the part to the center of the lands, the C1 and C2 dimensions.

Land Size Round-off is the value that the land size rounds up or down to. The IPC-7351 standards round land sizes to 0.05mm increments with the exception of micro-miniature component packages that are typically less than 1.6mm in size. The micro-miniature part land size round-off is set to 0.01mm increments. In Figure 4, the "X" & "Y" dimensions are rounded off in 0.05 mm increments. Even the land corner radius is rounded in 0.05 mm increments. When you export your PCB design layout database, all numbers for every design element should be in 0.05 mm increments. This greatly optimizes your PCB layout but also organizes all the graphics for best-in-class aesthetics for your PCB design layout.

Figure 4. Land place and size round-off.

**Solder Joint Goals** for toe are usually the outside the component lead with two exceptions: With the Jlead and molded body components, the toe is under the component body. The heel goals are normally on the inside of the component lead and the side goals are for both sides of the component lead. In Part 5 of this series I listed the component lead forms. Every lead form has its unique solder joint goal table. Here is a sample table for the Least, Nominal and Most "Toe, Heel and Side" goals and the placement courtyard excess for the gull wing component family. Notice the round-off factor is in 0.05 mm increments. See Table 1.

| Gull Wing Lead         | Least<br>Level C | Nominal<br>Level B | Most<br>Level A |

|------------------------|------------------|--------------------|-----------------|

| Toe (J⊤)               | 0.15             | 0.35               | 0.55            |

| Heel (J <sub>H</sub> ) | 0.25             | 0.35               | 0.45            |

| Side (J <sub>s</sub> ) | 0.01             | 0.03               | 0.05            |

| Round-off factor       | Round of         | ff to the ne       | arest 0.05      |

| Courtyard excess       | 0.1              | 0.25               | 0.5             |

Table 1. Gull-wing solder joint goal table.

When all of the tolerances, round-offs and solder joint goals are applied the end result is a perfect land pattern. See Figure 5.

Figure 5. Land pattern and component with tolerances.

If all the tolerances and solder joint goals were removed from the mathematical model, the component lead would be equal to the land size. This is the starting point for all land size calculations. Figure 6 illustrates a chip component (black outline) <u>without</u> tolerances, round-offs, or solder joint goals and the land size (cyan) without a toe, heel or side goal.

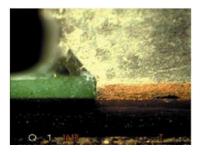

Figure 6. Land pattern and component.

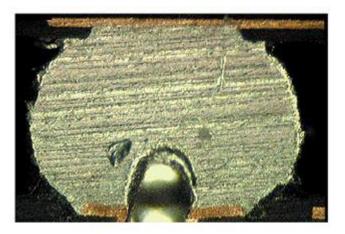

The resulting solder joint for a chip component should look similar to this picture. Note that the component terminal never touches the land. There must be solder paste between the component lead and the land to form the best solder joint. See Figure 7. Here's a note from the IPC J-STD-001D "Requirements for Soldered Electrical and Electronic Assemblies." **Section 4.14 Solder Connection:** All solder connections **shall** indicate evidence of wetting and adherence where the solder blends to the solder surface.

Figure 7. Chip solder joint.

# **Padstacks**

Padstack creation is something every CAD tool will eventually have to incorporate because it expedites and optimizes the construction of CAD libraries. The SMT padstack is easy to define:

Top land

Top solder mask

Top paste mask

Top assembly

Last week, I explained land calculation for SMT land patterns, so let's discuss plated through-hole calculations in this segment.

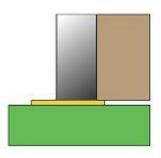

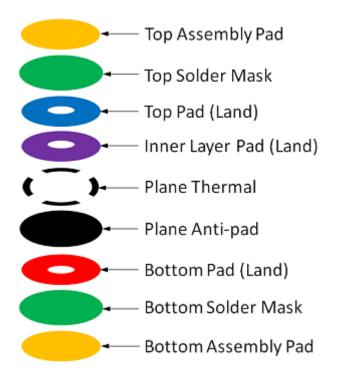

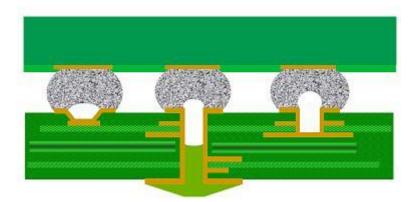

The through-hole (PTH) padstack is complex. See Figure 1 of a through-hole padstack.

Drill hole

Top assembly

Top solder mask

Top land

Inner land

Plane thermal relief

Plane anti-pad (clearance)

Bottom land

Bottom solder mask

Bottom assembly

The PTH padstack creation can be fully automated via the maximum lead diameter. See Figure 2.

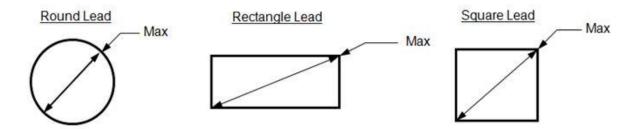

# Figure 2. Plated through-hole maximum lead size.

IPC-2222 Table 9-3 has a hole size calculation chart for maximum lead + level = minimum hole size.

| IPC-                    | 2222 Tabl   | e 9-3    |  |

|-------------------------|-------------|----------|--|

| Max Lead                | d + Level = | Min Hole |  |

| Level A Level B Level C |             |          |  |

| 0.25                    | 0.2         | 0.15     |  |

# IPC-2222, Table 9-3.

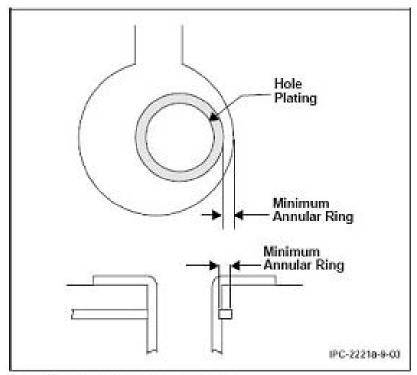

Once you calculate the hole size, add the minimum annular ring of 0.05 mm per IPC-2221 Table 9-2.

Figure 9-3 Internal Annular Ring

Table 9-2 Annular Rings (Minimum)

| Annular Ring         | Class 1, 2, and 3      |  |

|----------------------|------------------------|--|

| Internal Supported   | 0.025 mm [0.00098 in]  |  |

| External Supported   | 0.050 mm [0.00197 in]  |  |

| External Unsupported | 0.150 mm [0.005906 in] |  |

# Figure 3. IPC-2221 minimum annular ring.

Next we need to add the IPC-2221 Minimum Fabrication Allowance to the pad size in Table 9-1.

| IPC-2221 Table 9-1<br>Min Fabrication Allowance |     |     |                         |

|-------------------------------------------------|-----|-----|-------------------------|

|                                                 |     |     | Level A Level B Level C |

| 0.6                                             | 0.5 | 0.4 |                         |

# IPC-2221, Table 9-1.

So, the minimum annular ring X 2 + minimum fabrication allowance + maximum lead + hole over lead = pad diameter

Next we need to calculate the plane thermal relief ID, OD and spoke width sizes.

| Thermal Spoke Width = 60%     |

|-------------------------------|

| Hole Dia divided by Spoke Qty |

| Round up to nearest 0.05 mm   |

| Therma  | I ID over H          | ole Size |  |

|---------|----------------------|----------|--|

| Level A | el A Level B Level C |          |  |

| 0.6     | 0.4                  | 0.3      |  |

| Thermal | OD over H       | Hole Size |  |

|---------|-----------------|-----------|--|

| Level A | Level B Level C |           |  |

| 1       | 0.7             | 0.5       |  |

| Ther    | mal OD ov       | er ID  |

|---------|-----------------|--------|

| Level A | Level B Level ( |        |

| 0.4 mm  | 0.25 mm         | 0.2 mm |

# Figure 4. Thermal relief calculations.

The plane anti-pad or plane clearance is the same size as the thermal relief OD (outside diameter).

In both the SMT and PTH padstack, the IPC-recommended solder mask and paste mask size is 1:1 scale of the top and bottom land size. The PCB fabrication shop can automatically oversize (swell) the solder mask to any size necessary to insure high yield production per their specific manufacturing capabilities. This is where automation of padstack generation comes in. The entire concept is to generate a padstack that meets the environment class of your design specification.

The IPC-7251 through-hole land patterns have the capability of accommodating all three performance classifications.

# **Producibility Levels**

When appropriate, this standard will provide three design producibility levels of features, tolerances, measurements, assembly, testing of completion or verification of the manufacturing process that reflect progressive increases in sophistication of tooling, materials or processing and, therefore progressive increases in fabrication cost. These levels are:

Level A General Design Producibility – Preferred [Maximum land\lead to hole relationship]

Level B Moderate Design Producibility – Standard [Nominal landVead to hole relationship]

#### Level C High Design Producibility – Reduced [Least land\lead to hole relationship]

Producibility levels are not to be interpreted as a design requirement, but a method of communicating the degree of difficulty of a feature between design and fabrication/assembly facilities. The use of one level for a specific feature does not mean that other features must be of the same level. Selection should always be based on the minimum need, while recognizing that the precision, performance, conductive pattern density, equipment, assembly and testing requirements determine the design producibility level. The numbers listed within the tables of IPC-7251 are to be used as a guide in determining what the level

of producibility will be for any feature. The specific requirement for any feature that must be controlled on the end item shall be specified on the master drawing of the printed board or the printed board assembly drawing.

Download the IPC-7251 padstack charts here - AppNote 10835: IPC-7251 Padstack Charts

**Density Level A: Maximum Land/Lead to Hole Relationship** – The 'maximum' land pattern conditions have been developed to accommodate the most robust producability of the solder application method. The geometry furnished may provide a wider process window for solder processing. The level A land patterns are usually associated with low component density product applications.

**Density Level B: Nominal Land/Lead to Hole Relationship** – Products with a moderate level of component density may consider adapting the 'median' land pattern geometry. The median land patterns furnished for all device families will provide a robust solder attachment condition for most soldering processes and should provide a condition suitable for wave, dip, drag or reflow soldering.

**Density Level C: Least Land/Lead to Hole Relationship** – High component density typical of portable and hand-held product applications may consider the 'minimum' land pattern geometry variation. Selection of the minimum land pattern geometry may not be suitable for all product use categories.

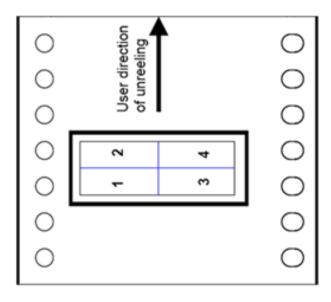

The "proportional" PTH padstacks are a mixture combination of all the IPC levels. Small holes use Level C and medium hole sizes use Level B and large hole sizes use Level A. When a hole size exceeds 2 mm, the proportional padstack annular ring will incrementally grow with every hole size. I have used the proportional padstacks for the past 20 years and it is proven technology that works. Its flexible flow is more compliant with the PTH components and their pin-pitch density. The main point is that proportional padstacks meet or exceed the IPC-7251 standard.

Note: the Producibility Levels are not necessarily related to the IPC Preformance Classifications, i.e., the IPC-7251 land patterns are capable of accommodating all three performance classifications.

# **IPC Performance Classifications**

Three general end-product classes have been established to reflect progressive increases in sophistication, functional performance requirements and testing/inspection frequency. It should be recognized that there may be an overlap of equipment between classes.

The end product user has the responsibility for determining the "use category" or "class" to which the product belongs. The contract between user and supplier shall specify the class required and indicate any exceptions or additional requirements to the parameters, where appropriate.

**Class 1 General Electronic Products** – Includes consumer products, some computer and computer peripherals, and hardware suitable for applications where the major requirement is function of the completed assembly.

**Class 2 Dedicated Service Electronic** – Products Includes communications equipment, sophisticated business machines, and instruments where high performance and extended life is required, and for which uninterrupted service is desired but not mandatory. Typically the end-use environment would not cause failures.

**Class 3 High-Reliability Electronic Products** – Includes all equipment where continued performance or performance-on-demand is mandatory. Equipment downtime cannot be tolerated, end-use environment may be uncommonly harsh, and the equipment must function when required, such as life support systems and other critical systems.

# **Zero Component Orientation**

A standard for component mechanical outlines and how they mount on a PCB is necessary to ensuring global commonality of design. In 2005 IPC and IEC (International Electrotechnical Commission) established a joint standard for land pattern geometries (IPC-7351/IEC 61188-5-1). To maintain a consistent method where these two important standards describe the component mechanical outlines and their respective mounting platforms, a single concept had to be developed that takes into account various factors within the global community.

The land pattern standards clearly define all the properties necessary for standardization and acceptability of a "One World CAD Library." The main objective in defining this CAD library is to achieve the highest level of electronic product development automation. This encompasses all the processes involved from engineering to PCB layout to fabrication, assembly, and test. The data format standards need this type of consistency to meet the efficiency that electronic data transfer can bring to the industry.

Many large firms have spent millions of dollars creating and implementing their own unique internal standards for their own electronic product development automation. These internal standards are proprietary to each firm and are not openly shared with the rest of the industry. The result is a massive duplication of effort that costs the industry millions of man-hours in waste and creates industry chaos and global non-standardization.

The land pattern standards IPC-7351 and IEC 61188-5-1 put an end to the "proprietary intellectual property" and introduced a world standard so every electronics firm can benefit from electronic product development automation. The data format standards IPC-2581 and IEC 61182-2 are an open database XML software code that is neutral to all the various CAD ASCII formats. For true machine automation to exist, the world desperately needs a neutral CAD database format that all PCB manufacturing machines can read.

# **Fixed Component Orientation**

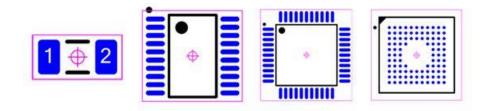

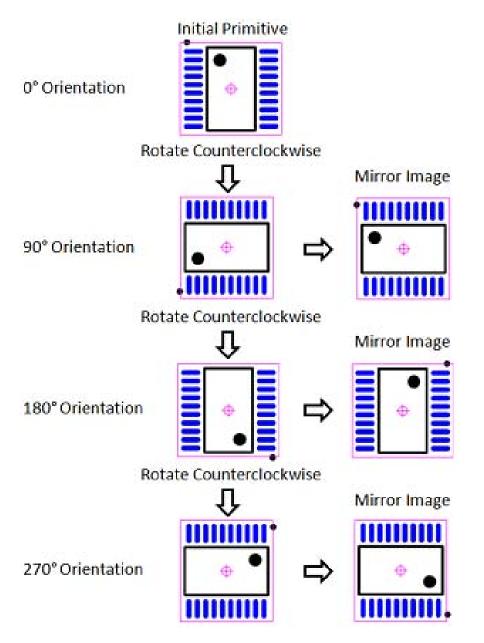

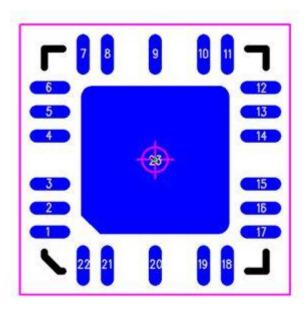

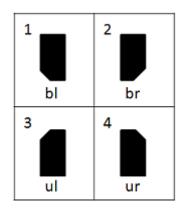

One of the factors in global standardization is that of establishing a CAD component description and land pattern standard that adopts a fixed zero component orientation so that all CAD images are built with the same rotation for the purpose of assembly machine automation. IPC-7351 indicates that in the CAD library, all pin 1 locations are in the upper left corner for multiple pin components and pin 1 on the left for 2-pin components. Figure 1 represents IPC-7351 default and IEC 61188-7 Level A zero component orientation.

Figure 1. IPC-7351 zero component orientation with pin 1 in upper left corner.

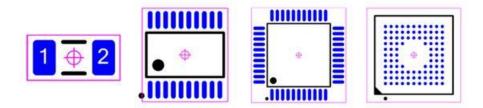

In May 2009, the IEC land pattern committee voted and approved a new Level B Zero Component Orientation and redefined the IPC-7351 Zero Orientation as level A. The new IEC 61188-7 defines Zero Component Orientation pin 1 locations in the bottom left corner, except for 2-pin components where pin 1 is on the left side, and labeled it level B. Figure 2 represents IEC 61188-7 level B zero component orientation.

Figure 2. IEC 61188-7 zero component orientation with pin 1 in lower left corner.

Since the basic rules allow two variations of levels in the description of the CAD system library, it is a mandatory requirement to define which level was used (level A or level B) for the component descriptions in the data file. This information is a mandatory requirement in the header of any file that incorporates land patterns using these principles of zero-based orientation. See Figure 3 for the level A zero orientation and machine rotation.

#### Figure 3. Example of "level A" orientation concepts.

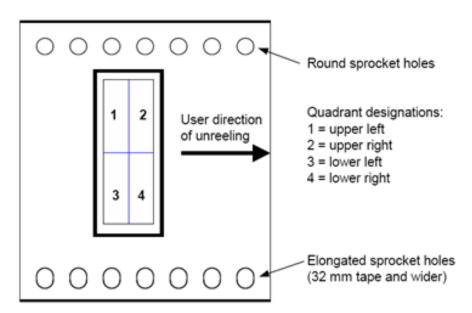

The industry association Electronics Industry Association (EIA) is responsible for component descriptions and tape and reel orientation in the EIA-481-D standard. EIA has tried valiantly to influence the industry by making good standards that describe the component outlines and how they should be positioned in the delivery system to the equipment on the manufacturing floor. But parts suppliers have either not adhered to the recommendations or have misunderstood the intent and provided their products in different orientations.